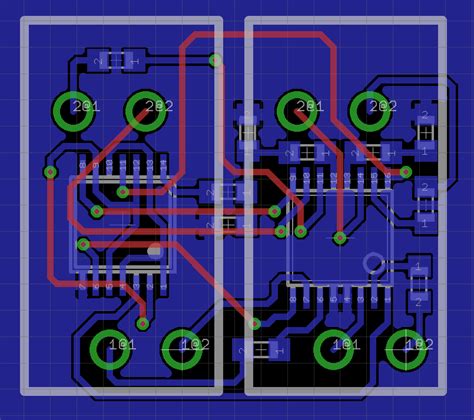

Introduction to High Frequency PCB Layout

High frequency PCB layout is a crucial aspect of designing printed circuit boards for applications that involve high-speed signals. As the demand for faster data transmission and higher bandwidth increases, designers must pay close attention to the layout of their PCBs to ensure optimal performance and minimize signal integrity issues. In this article, we will delve into the intricacies of high frequency PCB layout, exploring best practices, design considerations, and techniques to achieve robust and reliable high-speed designs.

What is High Frequency PCB Layout?

High frequency PCB layout refers to the process of designing printed circuit boards that can effectively handle high-speed signals. These signals typically have frequencies ranging from hundreds of megahertz (MHz) to several gigahertz (GHz). At such high frequencies, the behavior of signals on the PCB becomes more complex, and traditional layout techniques may not suffice. High frequency PCB layout aims to address the unique challenges associated with high-speed signals, such as signal integrity, electromagnetic interference (EMI), and power integrity.

Importance of High Frequency PCB Layout

Proper high frequency PCB layout is essential for several reasons:

-

Signal Integrity: High-speed signals are susceptible to various signal integrity issues, such as reflections, crosstalk, and attenuation. These issues can lead to data corruption, timing errors, and overall system malfunction. Careful PCB layout techniques help mitigate these problems and ensure the integrity of the transmitted signals.

-

EMI Reduction: High-speed signals can generate electromagnetic interference (EMI), which can interfere with the operation of nearby electronic devices. Effective high frequency PCB layout practices help minimize EMI emissions and ensure compliance with electromagnetic compatibility (EMC) regulations.

-

Power Integrity: High-speed circuits often have stringent power requirements. Maintaining a clean and stable power supply is crucial for optimal performance. High frequency PCB layout techniques help ensure proper power distribution, minimize voltage drops, and reduce power supply noise.

-

Reliability: A well-designed high frequency PCB layout enhances the reliability and longevity of the electronic system. By addressing signal integrity, EMI, and power integrity concerns, designers can create robust and dependable products that can withstand the rigors of high-speed operation.

High Frequency PCB Layout Considerations

When designing high frequency PCBs, several key considerations must be taken into account to ensure optimal performance. These considerations include material selection, trace geometry, impedance matching, grounding, and shielding.

Material Selection

The choice of PCB material plays a significant role in high frequency design. The dielectric constant (Dk) and dissipation factor (Df) of the material directly impact signal propagation and loss. For high-speed applications, it is recommended to use low-loss materials with a stable dielectric constant over the desired frequency range. Some commonly used materials for high frequency PCBs include:

- Rogers RO4000 series

- Isola I-Tera MT40

- Nelco N4000-13SI

- Panasonic Megtron 6

These materials offer excellent high-frequency performance, low dielectric loss, and good thermal stability.

Trace Geometry

Trace geometry is another critical aspect of high frequency PCB layout. The width, thickness, and spacing of traces directly influence the characteristic impedance and signal integrity. Some key considerations for trace geometry include:

-

Controlled Impedance: Traces should be designed to have a specific characteristic impedance, typically 50 ohms for single-ended signals and 100 ohms for differential pairs. Impedance matching is crucial to minimize reflections and ensure proper signal transmission.

-

Trace Width and Thickness: The width and thickness of traces should be carefully calculated based on the desired impedance and the PCB material properties. Thinner traces are generally preferred for high-speed signals to minimize parasitic capacitance and inductance.

-

Trace Spacing: Adequate spacing between traces is necessary to minimize crosstalk and electromagnetic coupling. The spacing should be determined based on the signal rise time, frequency, and the acceptable level of crosstalk.

-

Length Matching: For critical high-speed signals, such as clock lines or differential pairs, trace lengths should be matched to ensure equal propagation delays and minimize skew.

Grounding and Power Distribution

Proper grounding and power distribution are essential for maintaining signal integrity and reducing EMI in high frequency PCBs. Some best practices include:

-

Ground Planes: Use solid ground planes to provide a low-impedance return path for high-speed signals. Ground planes help minimize ground bounce and reduce EMI.

-

Power Planes: Dedicate separate power planes for different supply voltages to ensure a clean and stable power distribution. Use appropriate decoupling capacitors near power pins to minimize power supply noise.

-

Via Placement: Place vias strategically to minimize inductance and provide efficient current return paths. Avoid long via stubs, which can cause reflections and degrade signal quality.

-

Split Planes: In mixed-signal designs, use split planes to isolate sensitive analog circuitry from noisy digital sections. This helps prevent crosstalk and maintains signal integrity.

Shielding and EMI Reduction

Shielding and EMI reduction techniques are crucial in high frequency PCB layout to minimize electromagnetic interference and ensure EMC compliance. Some effective methods include:

-

Shielding Cans: Use shielding cans or enclosures to isolate sensitive components or high-frequency modules from external EMI sources.

-

Grounding Gaskets: Implement grounding gaskets around connectors and openings to provide a low-impedance path for EMI currents and prevent radiation leakage.

-

Filtering: Use appropriate filtering techniques, such as ferrite beads or LC filters, to suppress high-frequency noise on power lines and signal paths.

-

Spread-Spectrum Clocking: Employ spread-spectrum clocking techniques to reduce the peak energy of high-frequency signals and minimize EMI emissions.

High Frequency PCB Layout Techniques

To achieve optimal high frequency PCB layout, designers can employ various techniques and best practices. These techniques help address signal integrity, EMI, and power integrity concerns.

Microstrip and Stripline Transmission Lines

Microstrip and stripline transmission lines are commonly used in high frequency PCB layout to control impedance and minimize signal reflections. Microstrip lines are traces on the outer layer of the PCB, with a ground plane beneath them. Stripline traces are sandwiched between two ground planes, providing better shielding and reduced crosstalk compared to microstrip lines.

When designing microstrip or stripline transmission lines, consider the following:

-

Impedance Calculation: Use appropriate equations or simulation tools to calculate the required trace width and spacing for the desired characteristic impedance.

-

Trace Thickness: Choose a trace thickness that minimizes skin effect losses and ensures manufacturability.

-

Dielectric Thickness: Select an appropriate dielectric thickness between the trace and the ground plane to achieve the desired impedance and minimize losses.

Differential Pair Routing

Differential signaling is widely used in high-speed digital interfaces, such as USB, PCIe, and HDMI. Differential pairs consist of two traces carrying complementary signals, which helps reduce EMI and improve noise immunity. When routing differential pairs, consider the following guidelines:

-

Trace Spacing: Maintain a consistent spacing between the traces of a differential pair to ensure equal impedance and minimize skew.

-

Length Matching: Match the lengths of the differential pair traces to maintain signal integrity and minimize timing skew.

-

Coupling: Ensure sufficient coupling between the differential pair traces to maintain the desired differential impedance and reduce common-mode noise.

-

Avoid Discontinuities: Minimize discontinuities, such as vias or sharp bends, along the differential pair path to prevent reflections and maintain signal integrity.

Via Optimization

Vias are essential for connecting traces on different layers of a PCB, but they can introduce discontinuities and degrade signal quality at high frequencies. To optimize via performance, consider the following techniques:

-

Via Size: Use smaller via sizes to minimize parasitic inductance and capacitance. However, ensure that the via size is manufacturable and reliable.

-

Via Stubs: Minimize the length of via stubs to prevent reflections and resonances. Consider using blind or buried vias to reduce stub lengths.

-

Via Shielding: Implement via shielding techniques, such as ground vias or coaxial vias, to provide a low-impedance return path and reduce EMI.

-

Via Stitching: Use via stitching around high-speed traces to create a closely-spaced ground return path and minimize ground bounce.

Component Placement

Proper component placement is crucial for optimizing high frequency PCB layout. Consider the following guidelines:

-

Decoupling Capacitors: Place decoupling capacitors as close as possible to the power pins of high-speed components to minimize power supply noise and ensure a clean power delivery.

-

Sensitive Components: Position sensitive analog components, such as oscillators or precision amplifiers, away from noisy digital circuitry to minimize crosstalk and interference.

-

High-Speed Interfaces: Locate high-speed interfaces, such as USB or PCIe connectors, close to the edge of the PCB to minimize trace lengths and reduce signal degradation.

-

Component Orientation: Orient components to minimize the length of high-speed traces and avoid unnecessary crossovers or vias.

Simulation and Verification

To ensure the integrity of high frequency PCB layouts, designers often employ simulation and verification tools. These tools help analyze signal integrity, power integrity, and EMI performance before the PCB is fabricated.

Signal Integrity Simulation

Signal integrity (SI) simulation tools, such as Ansys SIwave or Cadence Sigrity, allow designers to analyze the behavior of high-speed signals on the PCB. These tools can help identify issues like reflections, crosstalk, and attenuation, and provide insights for optimizing the layout.

SI simulation typically involves the following steps:

-

Schematic Capture: Create a schematic of the high-speed circuitry, including components, interconnects, and terminations.

-

Layout Extraction: Extract the physical layout information, such as trace geometries, layer stackup, and material properties, from the PCB design software.

-

Simulation Setup: Define the simulation parameters, such as signal rise times, data rates, and termination conditions.

-

Analysis: Run the simulation and analyze the results, including eye diagrams, S-parameters, and time-domain waveforms, to identify any signal integrity issues.

-

Optimization: Iterate on the layout based on the simulation results to improve signal integrity and meet the desired performance criteria.

Power Integrity Simulation

Power integrity (PI) simulation tools, such as Ansys SIwave or Cadence Sigrity, help analyze the power distribution network (PDN) of a high frequency PCB. These tools can identify issues like voltage drops, power supply noise, and resonances, which can impact the performance of high-speed components.

PI simulation typically involves the following steps:

-

PDN Modeling: Create a model of the power distribution network, including power and ground planes, decoupling capacitors, and via structures.

-

Simulation Setup: Define the simulation parameters, such as power supply voltages, current profiles, and frequency range of interest.

-

Analysis: Run the simulation and analyze the results, including impedance plots, voltage noise waveforms, and current density maps, to identify any power integrity issues.

-

Optimization: Modify the PDN design, such as adding more decoupling capacitors or optimizing via placement, based on the simulation results to improve power integrity.

EMI Simulation

Electromagnetic interference (EMI) simulation tools, such as Ansys HFSS or CST Studio Suite, help predict the electromagnetic emissions from a high frequency PCB. These tools can assist in identifying potential EMI sources and ensuring compliance with EMC regulations.

EMI simulation typically involves the following steps:

-

3D Modeling: Create a 3D model of the PCB, including the layout, components, and enclosure.

-

Simulation Setup: Define the simulation parameters, such as frequency range, excitation sources, and boundary conditions.

-

Analysis: Run the simulation and analyze the results, including electric and magnetic field distributions, far-field radiation patterns, and emission spectra, to identify any EMI issues.

-

Optimization: Implement EMI reduction techniques, such as shielding, filtering, or layout modifications, based on the simulation results to minimize electromagnetic emissions.

High Frequency PCB Layout Checklist

To ensure a robust and reliable high frequency PCB layout, designers can refer to the following checklist:

- Select appropriate PCB materials with low dielectric loss and stable properties at high frequencies.

- Control trace impedance by calculating the required trace width and spacing based on the PCB material and desired characteristic impedance.

- Match trace lengths for critical high-speed signals, such as clock lines or differential pairs, to minimize skew and ensure signal integrity.

- Provide adequate spacing between high-speed traces to minimize crosstalk and interference.

- Use solid ground planes to provide a low-impedance return path for high-speed signals and reduce ground bounce.

- Implement proper power distribution techniques, such as separate power planes and decoupling capacitors, to ensure a clean and stable power supply.

- Optimize via placement and design to minimize inductance, avoid reflections, and provide efficient current return paths.

- Employ shielding techniques, such as shielding cans or grounding gaskets, to minimize EMI and ensure EMC compliance.

- Perform signal integrity, power integrity, and EMI simulations to analyze and optimize the high frequency PCB layout before fabrication.

- Follow best practices for component placement, such as locating decoupling capacitors close to power pins and positioning sensitive components away from noisy circuitry.

By following this checklist and applying the techniques discussed in this article, designers can create robust and reliable high frequency PCB layouts that meet the demanding requirements of modern electronic systems.

Frequently Asked Questions (FAQ)

-

What is the difference between microstrip and stripline transmission lines?

Microstrip transmission lines are traces on the outer layer of the PCB, with a ground plane beneath them. They offer easier access for probing and rework but are more susceptible to external interference. Stripline transmission lines are traces sandwiched between two ground planes, providing better shielding and reduced crosstalk but requiring more complex manufacturing processes. -

How can I calculate the characteristic impedance of a trace?

The characteristic impedance of a trace can be calculated using equations that take into account the trace width, thickness, dielectric constant of the PCB material, and the height of the trace above the ground plane. There are online calculators and PCB design software tools that can assist in determining the required trace dimensions for a specific characteristic impedance. -

What is the purpose of decoupling capacitors in high frequency PCB layout?

Decoupling capacitors are used to provide a local, low-impedance source of charge for high-speed components, such as processors or FPGAs. They help minimize power supply noise and ensure a clean and stable power delivery to the components. Decoupling capacitors should be placed as close as possible to the power pins of the components to be effective. -

How can I minimize crosstalk between high-speed traces?

To minimize crosstalk between high-speed traces, several techniques can be employed: - Increase the spacing between the traces to reduce electromagnetic coupling.

- Use ground traces or planes between adjacent high-speed traces to provide shielding.

- Route sensitive traces on different layers of the PCB to increase separation.

-

Use differential signaling, which helps cancel out common-mode noise.

-

What are some common EMI reduction techniques in high frequency PCB layout?

Common EMI reduction techniques include: - Using shielding cans or enclosures to isolate sensitive components or high-frequency modules.

- Implementing grounding gaskets around connectors and openings to provide a low-impedance path for EMI currents.

- Applying filtering techniques, such as ferrite beads or LC filters, to suppress high-frequency noise on power lines and signal paths.

- Employing spread-spectrum clocking to reduce the peak energy of high-frequency signals.

- Optimizing the PCB layout to minimize loop areas and provide proper grounding.

Conclusion

High frequency PCB layout is a critical aspect of designing modern electronic systems that operate at high speeds and frequencies. By understanding the unique challenges associated with high-speed signals and applying appropriate layout techniques, designers can create robust and reliable PCBs that maintain signal integrity, minimize EMI, and ensure optimal performance.

This article has covered the essential considerations for high frequency PCB layout, including material selection, trace geometry, grounding, power distribution, and shielding. We have also discussed various layout techniques, such as microstrip and stripline transmission lines, differential pair routing, via optimization, and component placement.

Furthermore, the importance of simulation and verification tools, such as signal integrity, power integrity, and EMI simulations, has been highlighted. These tools enable designers to analyze and optimize their layouts before committing to fabrication, saving time and costs.

By following the guidelines and best practices presented in this article, and utilizing the provided checklist, designers can navigate the complexities of high frequency PCB layout and create high-performance electronic systems that meet the ever-increasing demands of today’s applications.

Leave a Reply