Introduction to Etching Issues in Multilayer PCB Manufacturing

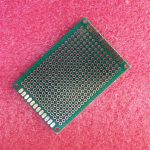

Multilayer printed circuit boards (PCBs) are essential components in modern electronics, enabling complex circuitry to be densely packed into compact devices. The manufacturing process for multilayer PCBs involves many precise steps, one of the most critical being etching. Etching is used to selectively remove copper from the PCB substrate to create the desired circuit pattern on each layer.

However, etching multilayer PCBs presents several challenges that can impact the quality, reliability, and yield of the final product. In this article, we will explore three key issues related to etching in multilayer PCB manufacturing:

- Overetching and underetching

- Etch factor control

- Alignment and registration

By understanding these issues and implementing best practices to mitigate them, PCB manufacturers can produce high-quality multilayer boards with consistent performance.

Issue 1: Overetching and Underetching

One of the primary challenges in etching multilayer PCBs is achieving the right amount of etching – removing just enough copper to create clean, well-defined circuit traces without compromising the integrity of the remaining copper. Two common problems that can occur are overetching and underetching.

Overetching

Overetching happens when too much copper is removed during the etching process, resulting in traces that are thinner than intended or even completely eaten away in some areas. This can be caused by several factors:

- Excessive etching time

- Overly aggressive etchant chemistry

- High etchant temperature

- Inadequate photoresist coverage or adhesion

The consequences of overetching include:

- Increased trace resistance

- Reduced current carrying capacity

- Potential open circuits

- Weakened mechanical strength

To prevent overetching, it’s important to carefully control the etching parameters and ensure the photoresist is applied properly. Using a more selective etchant that preferentially attacks copper over the photoresist can also help.

Underetching

Underetching is the opposite problem, where not enough copper is removed, leaving behind residual copper shorts between traces that should be isolated. Causes of underetching include:

- Insufficient etching time

- Weak or depleted etchant

- Low etchant temperature

- Thick or hardened photoresist

Underetched boards may suffer from:

- Shorted traces

- Excessive crosstalk

- Degraded signal integrity

- Reliability issues

Careful process control and regular etchant maintenance can help avoid underetching. Techniques like pulse plating can also be used to improve copper thickness uniformity.

The table below summarizes the causes and effects of overetching and underetching:

| Issue | Causes | Effects |

|---|---|---|

| Overetching | – Excessive etch time – Aggressive etchant – High temperature – Poor photoresist |

– Thin traces – Increased resistance – Open circuits – Weak spots |

| Underetching | – Short etch time – Weak etchant – Low temperature – Thick photoresist |

– Residual copper – Shorted traces – Crosstalk – Reliability issues |

Issue 2: Etch Factor Control

Another key consideration in multilayer PCB etching is the etch factor, which describes the ratio of vertical etch depth to horizontal etch undercut. Ideally, etching should proceed straight downward to create vertical sidewalls, but in practice there is always some degree of lateral etching that occurs beneath the photoresist edges.

Isotropic vs. Anisotropic Etching

The extent of this lateral etching depends on the isotropy of the etching process. Purely isotropic etching proceeds equally in all directions, resulting in curved sidewalls and significant undercut. Anisotropic etching is more directional, etching preferentially in the vertical direction to produce straighter sidewalls.

In multilayer PCBs, a high degree of anisotropy is desirable to maintain consistent trace widths and spacing between layers. This is especially important for high-density designs with fine pitch features.

Factors that influence etch isotropy include:

- Etchant chemistry

- Agitation

- Temperature

- Photoresist profile

Certain etchants, like cupric chloride, are more anisotropic than others. Spray etching can enhance anisotropy compared to immersion etching. Higher temperatures generally increase lateral etching, while a more vertical photoresist profile helps promote anisotropic etching.

Etch Factor Measurement and Control

Etch factor (EF) is defined as:

EF = 1 + 2U/T

Where U is the lateral undercut and T is the etch depth (i.e., the thickness of the copper being etched). An etch factor of 1 represents perfectly anisotropic etching with no undercut, while higher values indicate more lateral etching.

Measuring the etch factor involves cross-sectioning the etched traces and examining them under a microscope to determine the undercut and etch depth. This is typically done on a test coupon or dedicated PCB panel.

To control the etch factor, PCB manufacturers can adjust the etching parameters based on the measured values. For example:

- Increasing the spray pressure or using a more directional spray pattern to enhance anisotropy

- Lowering the etchant temperature to reduce lateral etching

- Optimizing the photoresist profile through exposure and development settings

The table below shows some typical etch factor values for different etching methods:

| Etching Method | Typical Etch Factor |

|---|---|

| Immersion etching | 2.0 – 3.0 |

| Spray etching | 1.2 – 2.0 |

| Bubble etching | 1.5 – 2.5 |

Issue 3: Alignment and Registration

A third critical issue in multilayer PCB etching is maintaining proper alignment and registration between the different layers. Each etched layer must line up precisely with the others to ensure reliable interconnections and prevent unintended shorts or opens.

Layer-to-Layer Alignment

Layer-to-layer alignment refers to the relative positioning of features on adjacent layers. Misalignment can occur due to several factors:

- Distortion or shrinkage of the PCB substrate during processing

- Inaccurate drilling or punching of registration holes

- Inconsistent or improper lamination

- Artwork or imaging errors

Misaligned layers can result in:

- Open circuits due to missed connections

- Short circuits due to unintended overlap

- Impedance mismatches

- Signal integrity issues

To minimize layer-to-layer misalignment, multilayer PCBs are typically constructed using a pin lamination process, where registration pins are used to precisely align the layers during lamination. The etched inner layers are also optically inspected prior to lamination to verify their alignment.

Interlayer Registration

Interlayer registration refers to the alignment of features between non-adjacent layers, such as from an inner layer to an outer layer. This is important for maintaining the continuity of vias and through-holes.

Factors that can affect interlayer registration include:

- Cumulative misalignment of multiple layers

- Drilling or routing errors

- Uneven lamination or press cycle

- Material movement or warpage

Interlayer registration issues can cause:

- Open or high-resistance connections at vias

- Unintended shorts between layers

- Reliability problems

Careful process control and regular calibration of drilling and routing equipment can help ensure good interlayer registration. Using materials with stable dimensions and low thermal expansion can also minimize registration errors.

The table below lists some common causes and effects of alignment and registration issues:

| Issue | Causes | Effects |

|---|---|---|

| Layer-to-layer misalignment | – Substrate distortion – Inaccurate drilling – Inconsistent lamination – Artwork errors |

– Open circuits – Short circuits – Impedance mismatches – Signal integrity issues |

| Interlayer registration errors | – Cumulative misalignment – Drilling/routing errors – Uneven lamination – Material movement |

– Open/high-resistance vias – Shorts between layers – Reliability problems |

FAQ

- What is the most common cause of overetching in multilayer PCBs?

Overetching is often caused by excessive etching time or an overly aggressive etchant chemistry. High etchant temperatures and inadequate photoresist coverage can also contribute to overetching.

- How can underetching be prevented?

To prevent underetching, it’s important to use a sufficiently active etchant and allow enough time for the etching process to complete. Regular etchant maintenance, such as replacing or replenishing the solution, can help ensure consistent etching performance. Proper photoresist application and exposure are also critical to avoid areas of hardened resist that may inhibit etching.

- What is the ideal etch factor for multilayer PCBs?

The ideal etch factor depends on the specific design requirements, but in general, a lower etch factor is desirable for multilayer PCBs to maintain consistent trace geometries between layers. An etch factor of 1.0 represents perfectly anisotropic etching with no undercut, but this is not practically achievable. Typical etch factors for multilayer PCBs range from 1.2 to 2.0, with spray etching providing the most anisotropic results.

- How can layer-to-layer alignment be verified in multilayer PCBs?

Layer-to-layer alignment is typically verified by optically inspecting the etched inner layers prior to lamination. This can be done using a high-magnification microscope or an automated optical inspection (AOI) system. The layers are checked for proper alignment of features like pads, traces, and registration marks. Any misalignment beyond the specified tolerances must be corrected before proceeding with lamination.

- What materials can help minimize registration errors in multilayer PCBs?

Using PCB materials with stable dimensions and low coefficients of thermal expansion (CTE) can help minimize registration errors caused by material movement or warpage during processing. Examples include polyimide, Teflon, and certain ceramic substrates. Choosing materials with closely matched CTEs for the different layers can also reduce stress and improve registration stability. Additionally, using a symmetrical stack-up and minimizing the overall thickness of the multilayer assembly can help prevent warpage and maintain good registration.

Conclusion

Etching is a critical process in the manufacturing of multilayer PCBs, and it presents several challenges that can impact the quality and reliability of the final product. Overetching and underetching, etch factor control, and alignment and registration are three key issues that must be carefully managed to ensure successful etching results.

By understanding the causes and effects of these issues and implementing best practices for process control and material selection, PCB manufacturers can optimize their etching processes to achieve high yields and consistent performance in multilayer PCBs. This includes regular monitoring and maintenance of etching parameters, using appropriate etchant chemistries and equipment, and selecting PCB materials with stable properties.

As electronic devices continue to become more complex and miniaturized, the demand for high-density multilayer PCBs will only increase. Mastering the challenges of multilayer PCB etching will be essential for manufacturers to stay competitive and meet the evolving needs of their customers.

Leave a Reply